CAST

Woodcliff Lake, NJ 07677 [email protected]

+1 201.391.8300

https://www.cast-inc.com/

Automotive IMFAS SoC by RANiX Features CAST TSN Ethernet Switch for Smart Vehicle Networking - News

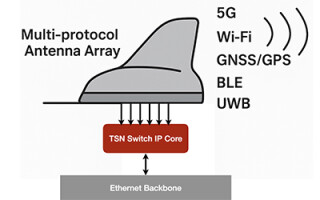

September 09, 2025Woodcliff Lake, New Jersey. CAST recently announced that its TSN Switch IP core is now integrated by RANiX Inc.’s new automotive Integrated Micro Flat Antenna System (IMFAS) system on chip (SoC). The IMFAS SoC operates a multi-element antenna array through synchronizing the wireless signals required for smart vehicles, including the 5G, WiFi, GNSS/GPS, BLE, and UWB protocols by securely and proficiently routing them to a central processing unit through the in-vehicle Ethernet network.

Pioneering Post-Quantum Security - News

January 16, 2025Woodcliff Lake, New Jersey. CAST announces its upcoming KiviPQC-KEM IP core and seeks the involvement of early adopters for product evaluations. Integrating the Module-Lattice Key Encapsulation Mechanism (ML-KEM) specified in the NIST FIPS 203 standard, this marks CAST's first step in applying post-quantum cryptography (PQC) algorithms to secure SoC designs.

CAST Adds New SafeSPI Controller to its Functional Safety IP Core Product Line - News

November 20, 2024The first such complete core is ideal for protected sensor/processor communication and joins CAST’s industry-leading set of ISO 26262 and other automotive cores

CAST Joins Forces with KiviCore to Deliver Next-Gen IP Cores for Quantum-Safe Security - News

November 13, 2024Woodcliff Lake, New Jersey. Recently, CAST and KiviCore announced a collaboration to deliver IP cores for post-quantum cryptographic hardware engines. With large-scale quantum computing on the horizon, the idea of post-quantum cryptography (PQC) is evolving to provide secure data solutions resistant to quantum-based cyber threats.

The Road to RISC-V Summit: CAST to Highlight 32-bit Solutions in Functional Safety and Ultra-Low Power - Blog

October 18, 2024During this year’s RISC-V Summit, CAST will be in booth S13 demonstrating its processors offered in ASICs or FPGAs for embedded systems, Internet of Things edge devices, industrial control systems, automotive, and aerospace applications. CAST’s RISC-V IP core line features processors focused on competitive 32-bit solutions in Functional Safety and Ultra-Low Power.

CAST and Ubilite Team-Up at the RISC-V Summit - News

November 08, 2023RISC-V Summit, Santa Clara, California. According to CAST, Ubilite, Inc. has licensed a RISC-V IP core for its next generation of Wi-Fi chipsets with an ultra-low power consumption rivaling Bluetooth Low Energy. Peter Gammel, Chief Executive Officer, Ubilite said, “We expect the RISC-V processor core we’ve licensed from CAST to help us maintain — and extend — the advantages of our low-power Wi-Fi SoCs over competing IoT products.”

embedded world 2023 Best in Show Winners: Processing & IP - Product

March 13, 2023Winners have been chosen based on a 15-point rubric that considers solutions’ Design Excellence (5 points), Relative Performance (5 points), and Market Impact/Disruption (5 points).