Check out preemptive scheduling in abstract RTOS modeling

March 17, 2015

Model-based designs are often the method of choice when dealing with critical systems as well as high quality systems. This often removes some of the...

Model-based designs are often the method of choice when dealing with critical systems as well as high quality systems. This often removes some of the implementation details, such as execution times and scheduling mechanisms. In system-level or model-based design methodologies, it’s become difficult to deal with events that require preemptive scheduling.

Preemptive scheduling is actually an act of temporarily interrupting a task that’s carried out by a system without requiring task cooperation and with the intent to resume that task at a later time. The time period for which a process is allowed to run in a preemptive multitasking system is generally called the time slice. The scheduler is run once every time slice to choose the next process. If the time slice is too short then the scheduler will consume too much processing time.

An interrupt will allow a switch between processes when their time slices expire, effectively allowing the processor’s time to be shared between a number of tasks, giving the illusion that it’s dealing with these tasks simultaneously, or concurrently. A multitasking operating system can control such a design.

We’ve evaluated a scenario of priority-based preemptive scheduling resources using VisualSim Architect, which provides a wide range of support for RTOS scheduling. Figure 1 is a sample that resembles a preemptive scheduler resource with multiple tasks. Here, we show three different tasks started at time intervals of 3, 6, and 9 seconds, respectively. The time slice for each task is 3 seconds.

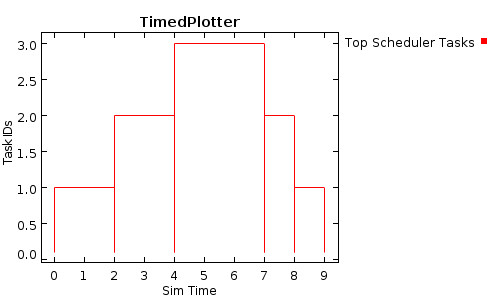

This model contains three independent processes that are being executed on the single scheduler. The scheduler is a dispatch unit and the actual deployment can be a microprocessor, DSP, FPGA, or ASIC. The model will evaluate the response time for the different tasks with a preemptive scheduling scheme, with different priority levels, arrival rates, and processing times. Priority is given for each process, which starts from 1 to 3, with the higher number getting the higher priority. Figure 2 shows the plot diagram for this sequence without considering preemption.

Process 1 will start at the 0.0 second mark, with a time slice of 3 seconds. Process 2 will start at 2.0 seconds with a 3.0 second time slice, and Process 3 starts at 4.0 seconds with a 3.0 second time slice.

Looking at the plot, the Process 1 will complete its processing of the scheduler resource within the 3 second time slice, and Process 2 should have started at 2.0 seconds. However, it’s delayed because of Process 1, which doesn’t complete until the 3 second mark. Similarly, Process 3 begins after a 2 second delay, waiting for Process 2 to complete.

Figure 3 is the task plot, showing when the scheduler resource is considered as a preemptive scheduler. Here, Process 1 starts in the scheduler at 0.0 and the task time/time slice allowed is 3.0 seconds. Hence, before completion of Process 1, Process 2 begins at 2.0 seconds because of its higher priority.

In this case, Process 1 is interrupted temporarily and Process 2 began. Similarly before the completion of Process 2, Process 3 will start (at the 4.0-second mark) because of its higher priority. When Process 3 completes in the scheduler resource, the next higher priority task in queue – Process 2 – will complete its cycle. It’s important to note that, even though Process 1 and Process 2 are interrupted, the total processing time is still 3.0 seconds for both as they complete the task later.

Preemptive multitasking allows the system to reliably guarantee that each process receives a regular slice of operating time. It also allows the system to rapidly deal with important external events like incoming data, which might require the immediate attention of one or another process.

K R Ranjith is an EDA application engineer, specializing in VisualSim system-level products at Mirabilis Design, located in Bengaluru, India. He has many years of expertise in system-level modeling, simulation, and development. Mr. Ranjith has been involved in various system-level model development projects with the defense sector, aerospace corporations, and multinational semiconductor companies in India. He completed his MS in Electronics from Kuvempu University and a Diploma in FPGA design and verification.