Importance of Hierarchical DFT implementation in maximizing the SoC - throughput ? Part - I

November 24, 2020

Story

Advanced Design For Test(DFT) techniques provides efficient test solutions to deal with higher test cost, higher power consumption, test area, and pin count at lower geometries.

Advanced Design For Test(DFT) techniques provides efficient test solutions to deal with higher test cost, higher power consumption, test area, and pin count at lower geometries by improving the controllability and observability of the sequential flops. In turn, this improves the yield on SoC. Reliability and testability are important factors in today's ASIC world.

SoCs are nothing but integrated circuit that integrate multiple processor cores, microcontrollers, interfaces, DSPs (digital signal processors), and memories on a single silicon substrate. In this era, it is one of the most important parts of any digital system because it helps in saving power, cost, and space.

A core is nothing but intellectual property or IP Cores of the SoC design companies. SoC design companies supply tests for the core and the SoC designer provides the test access to a core embedded on the chip. It is the hierarchical level at which wrapper chains are inserted by inserting the wrapper structure with test logic. We can minimize the core test problem and can reduce the top-level pin count of the SoC.

This paper gives a brief about the importance of Hierarchical DFT techniques, which utilizes wrapper chains to overcome the problems of testing large SoC design. It significantly reduces the ATPG test time, memory footprint, and pin count. Ultimately, it reduces the time to market.

Test Core Wrapper

For DFT, each core can be tested separately before SoC level integration. While performing integration, when they are configured in internal test mode, the core’s internal logic can be tested separately or in a group. However, when configured in the external test mode, the surrounding logic of the core can be tested. By doing so, our main concern is to divide the SoC test in a different configuration, to greatly reduce the pattern generation effort and in turn to reduce test time.

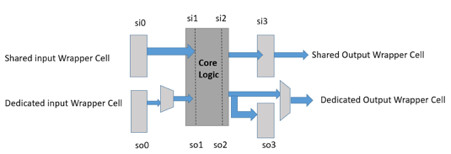

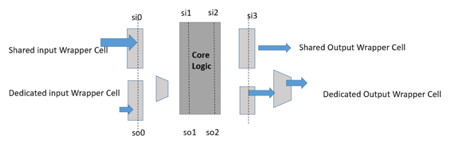

Wrapper Cell Structure

Test wrapper modes

Inward-facing or INTEST mode

In INTEST mode, by driving the inputs from the input wrapper cells, we test the partition and outputs are captured through output wrapper cells. This is completed by disabling the scan chain outside the core. It facilitates the isolated testing of the partitioned core with ATPG. During capture, input wrapper cells are shifted with a separate input wrapper scan enabled signal, which avoids x capturing from outside the partition. Whereas output wrapper cells capture the internal state of the partitions.

(Figure [2]: Inward Facing (Intest) Mode)

Outward-facing or EXTEST mode

In EXTEST mode, wrappers are enabled and configured to drive and capture data outside of the design. It essentially disables the internal chains by bypassing it in this mode. Hence, it reduces ATPG test time as well. To test the top-level logic between the partition and unwrapped logic, we can use this mode. During the capture stage, values are being captured by input wrapper cells outside the partition and the output wrapper cells shift during capture to avoid capturing x’s from inside the partition’s un-driven internal scan chains.

(Figure [3]: Outward Facing (Extest) Mode)

Hierarchical DFT Methodology

(Figure [4]: Hierarchical DFT Implementation (From Core to Chip level))

Large design issues like tool memory, large ATPG run time, and pin limitations can be resolved by Hierarchical DFT techniques. In this approach, the chip can be divided into multiple smaller pieces or cores, which can be efficiently accessed and processed. It results in a reduction in the pin count, memory and test run time due to patterns being generated at the core level. It is also possible to run cores in parallel.

Whenever a core is configured in internal mode, input wrappers launch into the core, and output wrappers observe the core output. In this case, core logic within the wrapper boundaries is tested. All the chains are connected to the compressor it generates core level patterns that can be retargeted to the top level. It also facilitates patterns of the multiple cores to be merged. For external mode, all wrapper chains are connected to the core boundary and patterns are generated for the top level. When it comes to full-chip level all the wrapper chains and top-level chains connect to the top-level compressor.

Hierarchical DFT Flow

(Figure [5]: Test Access Mechanism)

Figure 5 shows that top-level pins are shared among individual core level compressor logic and top-level compressor logic. It results in a reduction in the top-level chip pins, which performs hierarchical DFT. Individual cores can be tested separately or it can be tested in parallel to reduce the test time. The scan is inserted at the block level. When the blocks are assembled at the top level, the chains can be connected in one of two ways: concatenated or direct to I/O. In the concatenated scan chain approach, scan chains from one block are concatenated with chains from another block.

Advantages/disadvantages of Hierarchical DFT:

Some of the advantages of using hierarchical DFT are:

- By using automated tools, we can assemble core level chains at the SoC level.

- If the core level chains are balanced, then it will be easy for tools to balance SOC level chains.

- By maintaining a limited number of pins for scan chains can be manageable.

- It provides more core- level channels.

- ATPG run time is less and requires less memory which leads to a significant reduction in test time.

Some of the disadvantages are:

- When the design containing multiple clock edges and cause shifting problems when traversing back and forth between the rising edge and falling edge triggered flops as the scan chains travel through the cores.

- To avoid the timing issues, we have to take care of different clock domains at the core level and SoC level by using lock-up latches.

- In case if, the timing problems raising at a single-core level can cause damage to all the other cores since the chains are using in multiple cores.

In this paper, we have explored the importance of wrappers and types of wrappers cells. As described, the wrapper features and functional access as well as the access of the wrapper over different blocks. We have seen the hierarchical DFT methodology using the wrappers and the interconnections of the wrapper cells around the core logic. Finally, we have mentioned the wrapper generation and how can we minimize the area and the performance impact using wrapper cores. The hierarchical core wrapper has a wide range of industrial usage and we have presented the results of using the wrapper cells. eInfochips is successfully providing DFT solutions for Large SoC’s using Hierarchical DFT Implementation for majority of their clients.

About the Authors

Sunil Bhatt

Sunil Bhatt is working as Senior DFT Engineer in the DFT BU, ASIC division, at eInfochips, an Arrow Company. He has more than 3.5 years of experience in Design for Testing, which includes working on 40nm, 28nm, 7nm , and 5 nm technology nodes as a part of SoC projects with different clients. He is handling block-level, and top-level DFT activities.

Chintan Panchal

Chintan Panchal is working as a Delivery Manager in the ASIC division at eInfochips, an Arrow company. He has more than 19 years of experience in ASIC DFT. Over the years, he has worked on various technology nodes, from 180nm to 7nm, handling different DFT tasks, and managing a team of engineers

B. Ashok Kumar

B. Ashok Kumar working as Senior DFT Engineer in DFT BU, ASIC division, at eInfochips, an Arrow Company. He has more than three years of experience in ASIC DFT, which includes working on various technology nodes, from 28nm to 7nm, handling a block level and top level DFT activities.

References

[1] https://www.eetimes.com/complex-soc-testing-with-a-core-based-dft-strategy/

[2] https://blogs.mentor.com/tessent/blog/2016/03/15/hierarchical-dft-how-to-do-more-more-quickly-with-fewer-resources

[3] https://wenku.baidu.com/view/6a7ed208763231126edb11b5

[4] https://www.researchgate.net/publication/4058353_Overview_of_the_ieee_P1500_standard

[6] https://www.edn.com/boost-dft-efficiency-for-large-socs/

[7] https://www.valpont.com/dft-core-wrapper-cells-from-dft-compiler-and-logicvision/pst/