Taking industrial display interfaces beyond FPGAs and closed systems

September 07, 2016

Image resolution in industrial control, surveillance, and healthcare systems continues to move from 720p HD to 1080p FHD and 4K UHD and beyond. As dis...

Image resolution in industrial control, surveillance, and healthcare systems continues to move from 720p HD to 1080p FHD and 4K UHD and beyond. As display resolution has progressed, it has also become sensible for medical and industrial OEMs that rely on high-resolution video to look for new cost-effective imaging solutions that allow for rapid upscaling in an energy-efficient implementation.

However, advances in display technology bring new kinds of challenges. For example, the bandwidth requirements of next-generation displays are quickly outstripping the capabilities of existing board-to-board interconnect solutions such as transistor-transistor logic (TTL) and low-voltage differential signaling (LVDS). TTL is limited in displays with resolutions above 640 x 480 (VGA), while the LVDS and LVDS Display Interface (LDI) are restricted by their point-to-point topology, limited transmission distances (10 m per the OpenLDI specification), and wire count. As a result, the move to UHD often results in difficult decisions for display OEMs and their customers related to cost, power consumption, and electromagnetic interference (EMI).

One solution to these challenges is the V-by-One HS (high speed) protocol, an open standard originally developed by THine Electronics, Inc. that supports the higher frame rates and resolutions required by next-generation flat panel displays. V-by-One is an electrical digital signaling interface specification that runs over twisted-pair copper cables, and uses a proprietary encoding scheme along with a clock data recovery (CDR) and serializer/deserializer (SerDes) technology to deliver up to 3.75 Gbps throughput over as many as 32 lanes, depending on the bit width required for color and control. For panel and TV manufacturers migrating from 720p (1366 x 768 pixels) to 4K2K UHD (3840 x 2160 pixels), the extra bandwidth provided by V-by-One eases the 16x data transmission requirements that result from an eight-fold increase in data size at twice the refresh rate. In the context of LVDS, V-by-One’s performance is the equivalent of moving from six- to 96-paired lines.

Shortfalls of FPGAs as frequency rates rise

In the past, equipment vendors with long product lifecycles have turned to field-programmable gate arrays (FPGA) as a solution for building scalability into their designs. With the adoption of higher frequency interfaces for newer panels, however, the viability of using FPGAs as a method for avoiding significant hardware or firmware changes is diminishing. Only specialized FPGAs have the ability to support a V-by-One-PHY today, which raises cost, and the use of an FPGA also results in additional space requirements and significant power consumption.

Another major challenge with FPGAs is image upscaling, as even with the integration of the V-by-One interface, implementing changes to improve existing content for new, higher display resolutions is costly and requires a long validation process since all components within the chip must be tested to ensure 100 percent accuracy and reliable performance.

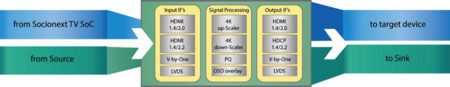

Alternatively, the Socionext HV series of application-specific standard products (ASSPs) supports V-by-One in addition to legacy interfaces such as HDMI and traditional LVDS inputs, along with a range of outputs for interfacing with the newest panel technologies (Figure 1). This I/O flexibility means current designs can use HV devices to support existing legacy displays while maintaining the ability to change later without significant qualification concerns. Since most system on chips (SoCs) now have HDMI-out capabilities, direct connection to 4K consumer panels is simple and provides image quality and cost advantages. Some members of the Socionext HV series also support a built-in picture quality engine to control brightness, color, contrast, depth, and more.

[Figure 1 | Socionext interface IPs support wide range of inputs.]

To generate the pixels required for higher content panels, significant processing power or video CODECs like H.264 or H.265, are often required, again increasing design complexity, power consumption, and cost. One of the most important requirements for this kind of technology is the ability to upscale from FHD (2K) to UHD (4K) without modification of the signal or content source, which save saves storage and bandwidth.

The Socionext HV solution also supports adjusting the amplitude of waveforms in 5 percent increments using parameter registers. This means EMI can be reduced based on specific usage conditions.

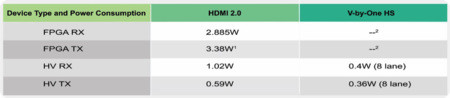

[Figure 2 | This comparison shows the power consumption of an FPGA-based imaging solution that includes the Texas Instruments SN65DP159 driver IC alongside Socionext’s HV ASSP. Notes: 1. The SN65DP159 measures out at 0.495 W (1.1 V * 150 mA +3.3 V * 100 mA), while the FPGA logic gates total 320k flip flops (FFs) receive and 325k FF transmit at 600 MHz clock frequency; 2. Determined by IP vendor and FPGA power usage, as well as external transmit and receive circuitry.]

[Figure 3 | Outlined here are the schematics of various HV ASSP product SKUs.]

Additional benefits for 2K to 4K up-scale conversion with “super resolution”

V-by-One HS offers high transmission quality even in noisy EMI conditions, and is quickly being adopted by high-end display manufacturers as a replacement for solutions based on the LVDS-based protocol. THine Electronics also recently announced V-by-One US (ultra speed), which offers a 4x speed improvement over HS, enabling 8K resolutions for cameras and displays while reducing cost. For operators of industrial control rooms, surveillance, and healthcare systems, the commercialization of these technologies will only continue to provide better performance at lower price points in upcoming design cycles.

Socionext Inc.

www.socionext.com