Avery Design Systems and CoMira Partner To Enable UCIe-Compliant Chiplet Design

January 25, 2023

News

Tewksbury, MA – January 25, 2023 – Avery Design Systems and CoMira Solutions are partnering to enable chiplet design using the UCIe (Universal Chiplet Interconnect Express) die-to-die interface standard, announced earlier this year, to provide interoperable chiplets and support an open chiplet ecosystem and universal interconnect at the package level.

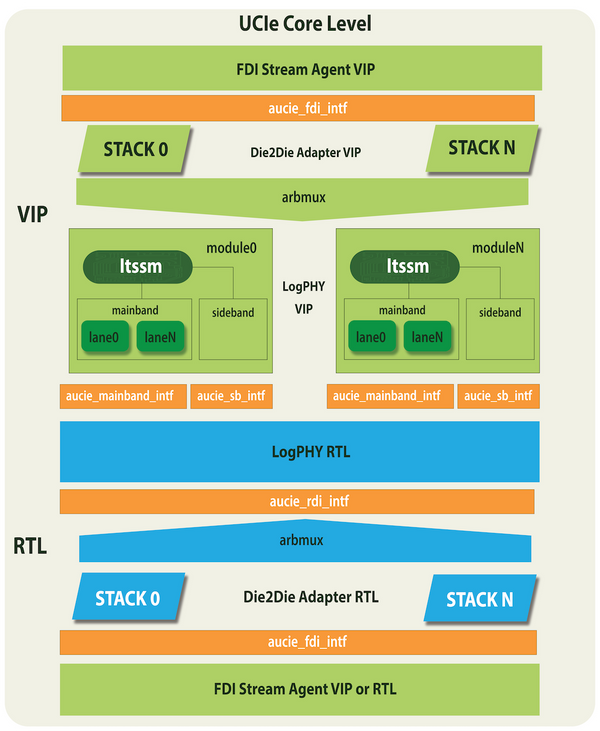

Using Avery’s verification IP (VIP) and functional verification platform, an offering that includes models and test suites that support pre-silicon verification of systems using UCIe, and CoMira’s high-speed protocol stack controller technology, currently under development, the companies will support the design and verification of multi-die systems using the UCIe standard.

“CoMira is leveraging its extensive experience in high-speed connectivity IP to provide a reliable and easy-to-integrate UCIe protocol stack technology for multi-die systems. By supporting UCIe for connectivity within the chiplet architecture, and CXL and PCIe for external interfaces, we provide the necessary element for full chiplet connectivity,” said Qasim Shami, founder and CEO of CoMira Solutions. “Avery provides the ideal verification environment to allow pre-silicon validation for the entire chiplet system.”

Avery’s functional verification platform is based on the company’s verification IP (VIP) portfolio which supports the pre-silicon validation of design elements. Their UCIe offering supports standalone UCIe die to die adapter and LogPHY verification with integrated PCIe and CXL VIP to run over the UCIe stack. Comprehensive protocol checkers, coverage, reference testbenches, and compliance test-suites using an open architecture are also supported by the platform.

Version 1.0 of the UCIe specification covers the UCIe Adapter and PHY with a die-to-die I/O physical layer, Die-to-Die protocols, and software stack utilizing the PCI Express® (PCIe®) and Compute Express Link™ (CXL™) industry standards with a protocol-agnostic raw transfer mode.